专栏名称: 芯片电源完整性与信号完整性设计

| 专注于SOC芯片级、系统级端到端SIPI设计;致力于分享SIPI领域硬核知识;可提供培训、咨询全系统SIPI设计;欢迎关注、分享、相互学习。 |

今天看啥

公众号rss, 微信rss, 微信公众号rss订阅, 稳定的RSS源

目录

相关文章推荐

|

广东民生DV现场 · 热搜第一!瑞幸咖啡,突然被曝!网友:喝不动了 · 2 天前 |

|

醒目视频 · 吃了一口就被灼伤了!很多佛山人都爱吃,近期千万注意 · 2 天前 |

|

|

醒目视频 · 收藏!叠滘龙船漂移开飙,观赛攻略来了 · 2 天前 |

|

羊城晚报 · 24小时内连震两次!凌晨河源再发3.0级地震 ... · 3 天前 |

今天看啥

›

专栏

›

芯片电源完整性与信号完整性设计

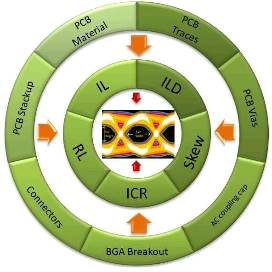

FoCoS/2.5D interposer SIPI电性能对比

芯片电源完整性与信号完整性设计 · 公众号 · · 2025-04-21 11:23

推荐文章

|

广东民生DV现场 · 热搜第一!瑞幸咖啡,突然被曝!网友:喝不动了 2 天前 |

|

醒目视频 · 吃了一口就被灼伤了!很多佛山人都爱吃,近期千万注意 2 天前 |

|

|

醒目视频 · 收藏!叠滘龙船漂移开飙,观赛攻略来了 2 天前 |

|

器械之家 · 倒查10年,多名医务人员职称被撤销 7 月前 |

|

江西省教育厅 · 春节|2025年春节,江西这里最热闹! 4 月前 |